- Design, Build and Analyze Your Own Custom Memories.

- Process Independent Algorithmic Generators.

- Extract Verilog from Layout.

- Automatic Path Pruning reduces SPICE Deck by 1000X.

The MegaCell Compiler (MCC) makes building all types of regular structures such as SRAMs, CAMs, DRAMs, Register Files, FIFOs, ROMs, PLAs, and even pad rings, fast and easy. The MegaCell Compiler is so fast that any size repetitive structure can be built in the comparable time it takes to load the data from the disk. Mere seconds for even multi-Mbit SRAMs.

Design and Build Custom

Memories

MCC is a Designer’s helper. It enables custom memory designers to quickly and easily construct and verify complete megacells from correct leaf cell layouts. MCC significantly reduces the effort required for full custom memory design.

More than just a simple tiler, MCC has a fully-hierarchical, relative-position tiling engine driven by a simple syntax. And if you don’t want to create the syntax, simply arrange the instances in the desired configuration and MCC will tell you what syntax creates that configuration. Because the tiler is relative and uses the abutment boundaries of the cells themselves, process shrinks and even technology retargeting are effortless once the leaf cells have been migrated.

MCC also provides a new scheme for programming rows, mux’s, etc., called via programming. Instead of relying on absolute coordinates; MCC automatically traces wire paths, finds overlaps, and automatically adds the appropriate vias. |

|

To complete the megacell, MCC propagates ports from leaf cells to the top level and renames them under programmatic control. Simply tell MCC to propagate the output ports on all of the sense amps, for example, and you get all of the ports from DOUT[0] to DOUT[31]. Because MCC handles tiling, via programming and

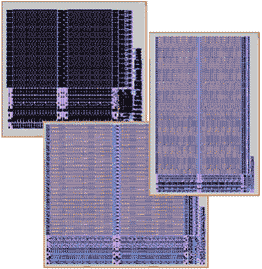

Figure 1-a. Figure 1-a.

Build a Family of SRAMs in a matter of minutes.

port propagation, megacells are easily parameterizable. MCC’s programming interface is so concise that a complete SRAM implementation takes less than 100 lines of code.

MCC allows the designer to parameterize the memory, i.e. build different sizes and configurations of the same basic memory structure simply by changing key parameters such as the number of rows or columns. This vastly speeds construction and verification, especially in large memory designs. By doing all construction and verification first on a very small structure, the |

|