Micro Magic, Inc. provides tools for all aspects of IC layout and design including specialized tools for Datapath Design, SoC Design Management and a powerful, specialized program for memories and other regular structures, MCC - Megacell Compiler.

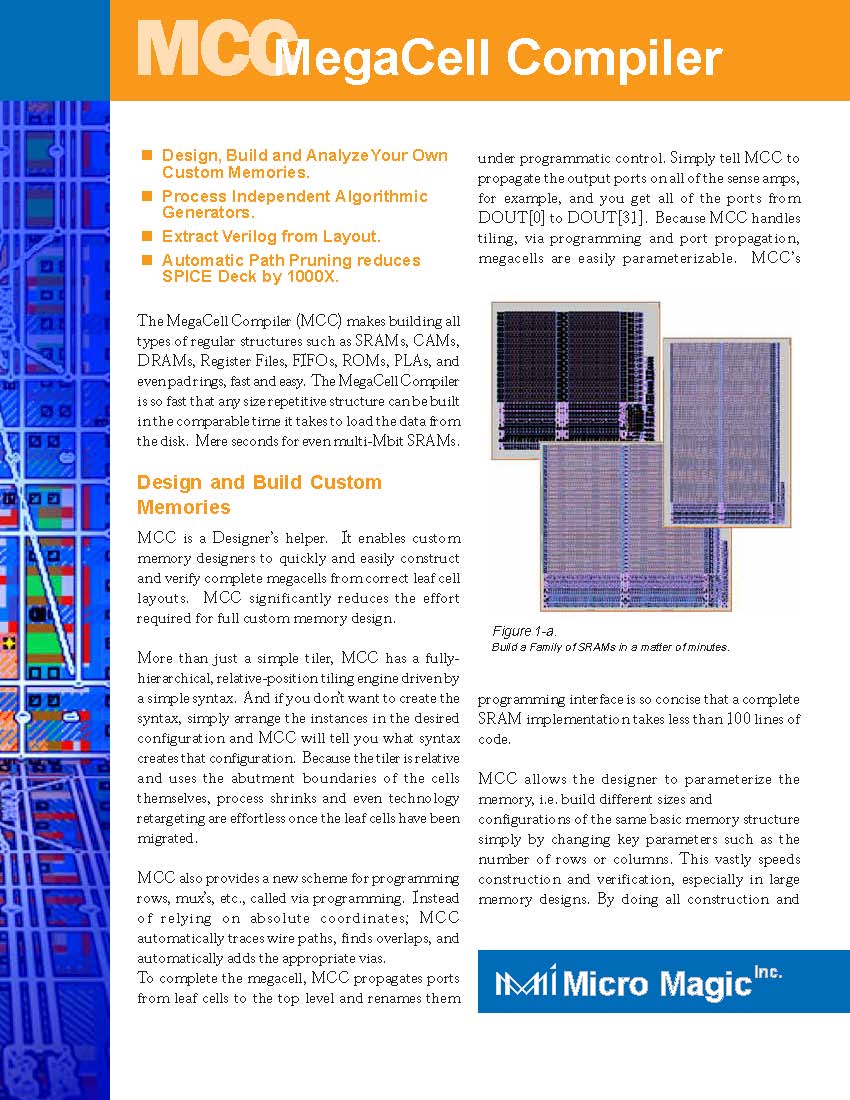

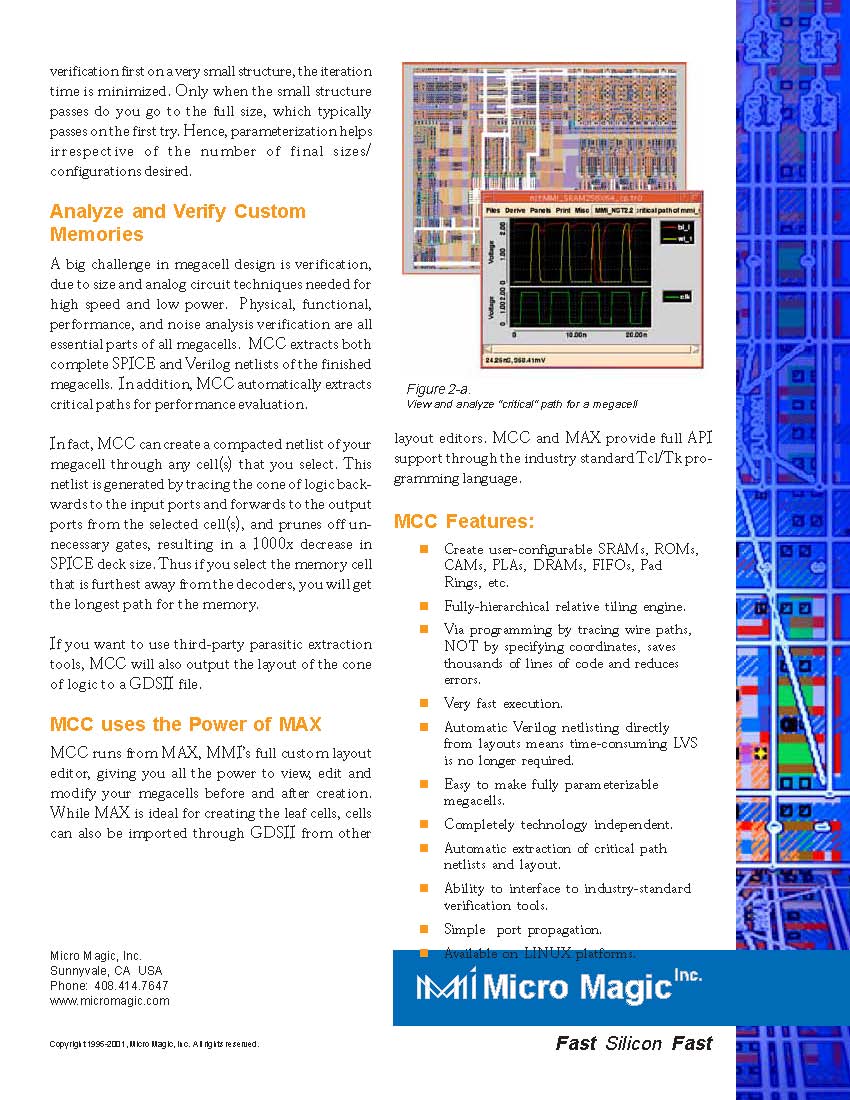

MegaCell Compiler (MCC) is an easy, powerful tool for building regular structures such as SRAMs, CAMs, DRAMs, Register files, FIFOs, ROMs, and PLAs.

MCC significantly reduces the effort required for building custom memories.

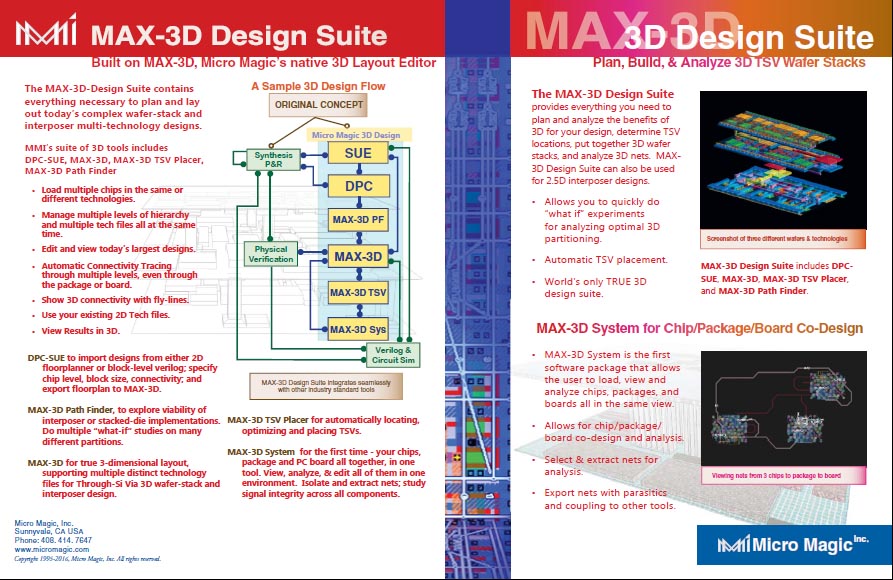

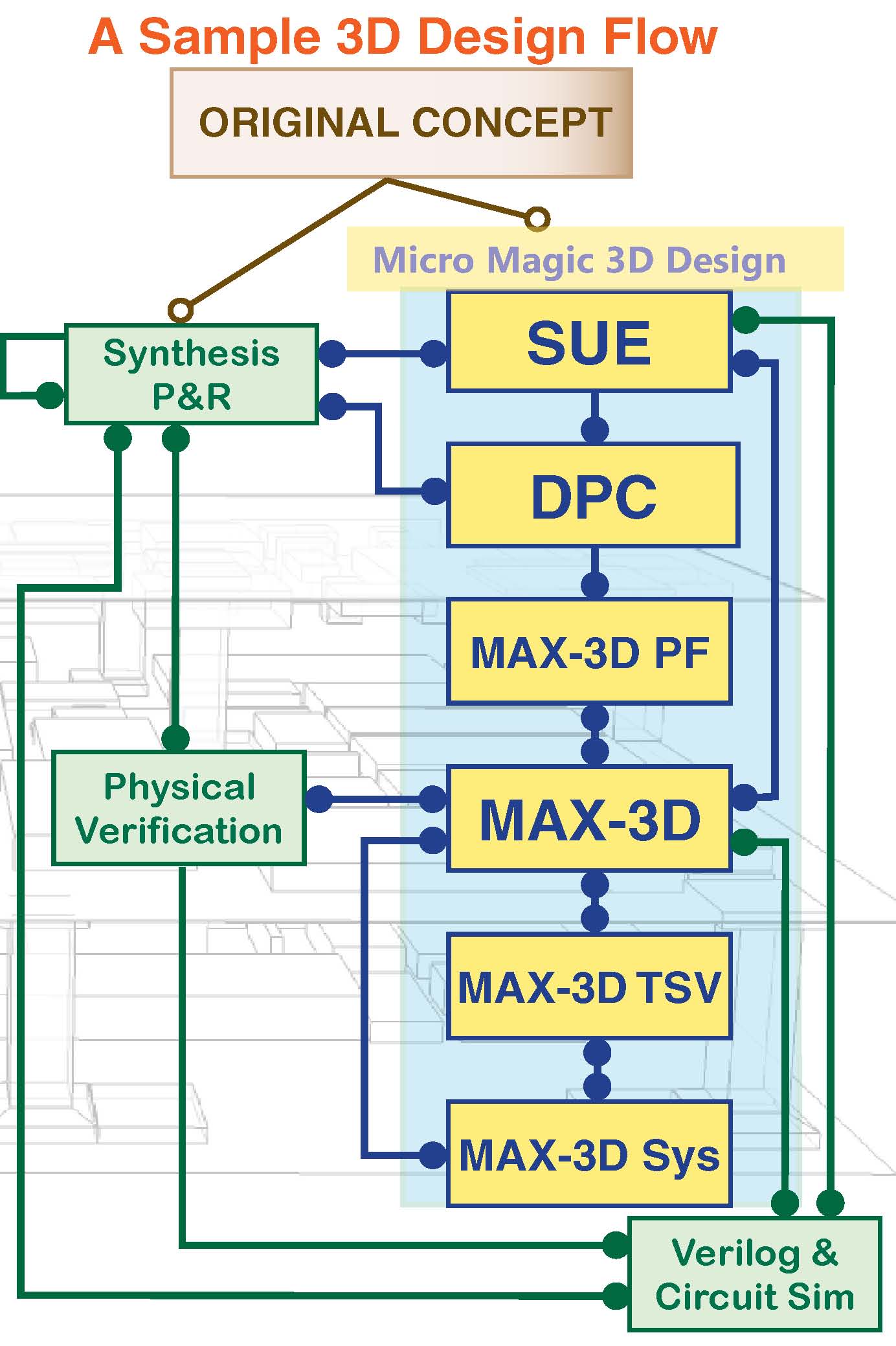

MMI MAX-3D Design Suite includes MAX-3D System, MAX-3D Path Finder, MAX-3D TSV Placer, and MAX-3D Layout.

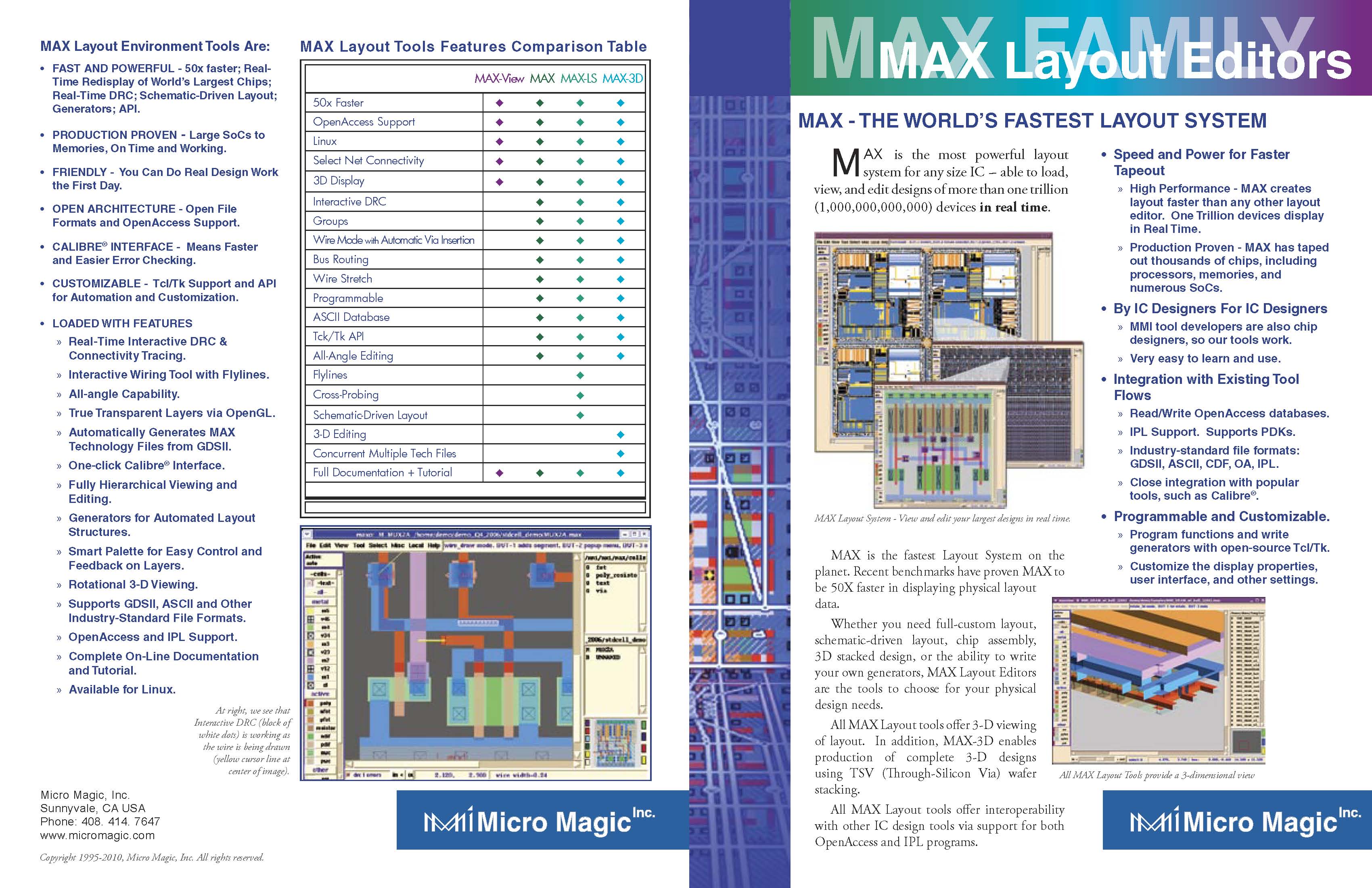

Fast, powerful, production-proven, easy to use layout tools.

Full-custom layout, schematic-driven layout, chip assembly, 3D stacked designs and more for all your physical design needs.

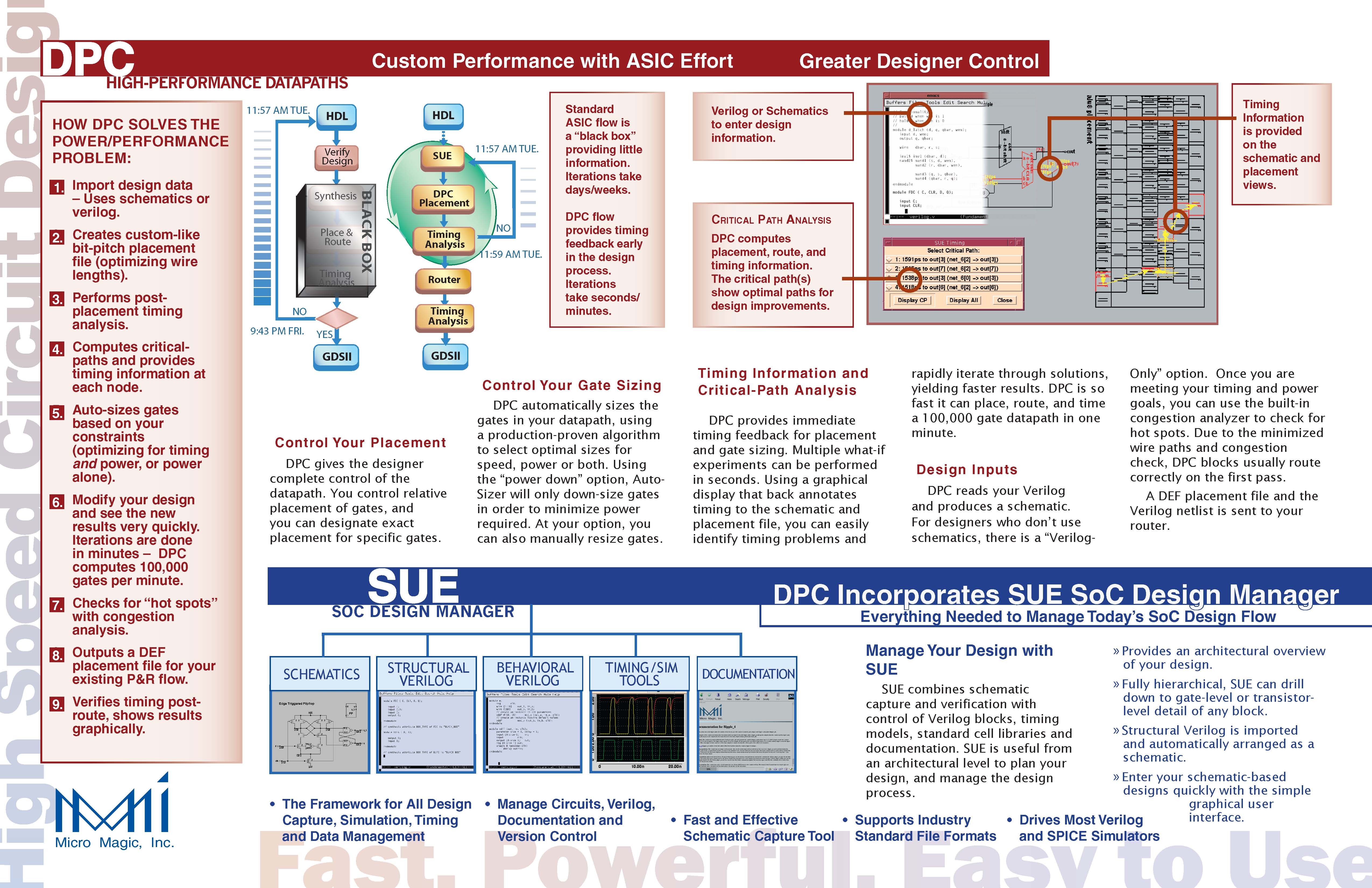

SUE SoC Design Manager Everything needed to manage today's SoC Design Flow

SUE combines Verilog, Schematic Capture, Documentation, Timing and Simulation tools to plan and manage your SoC project. More on SUE...

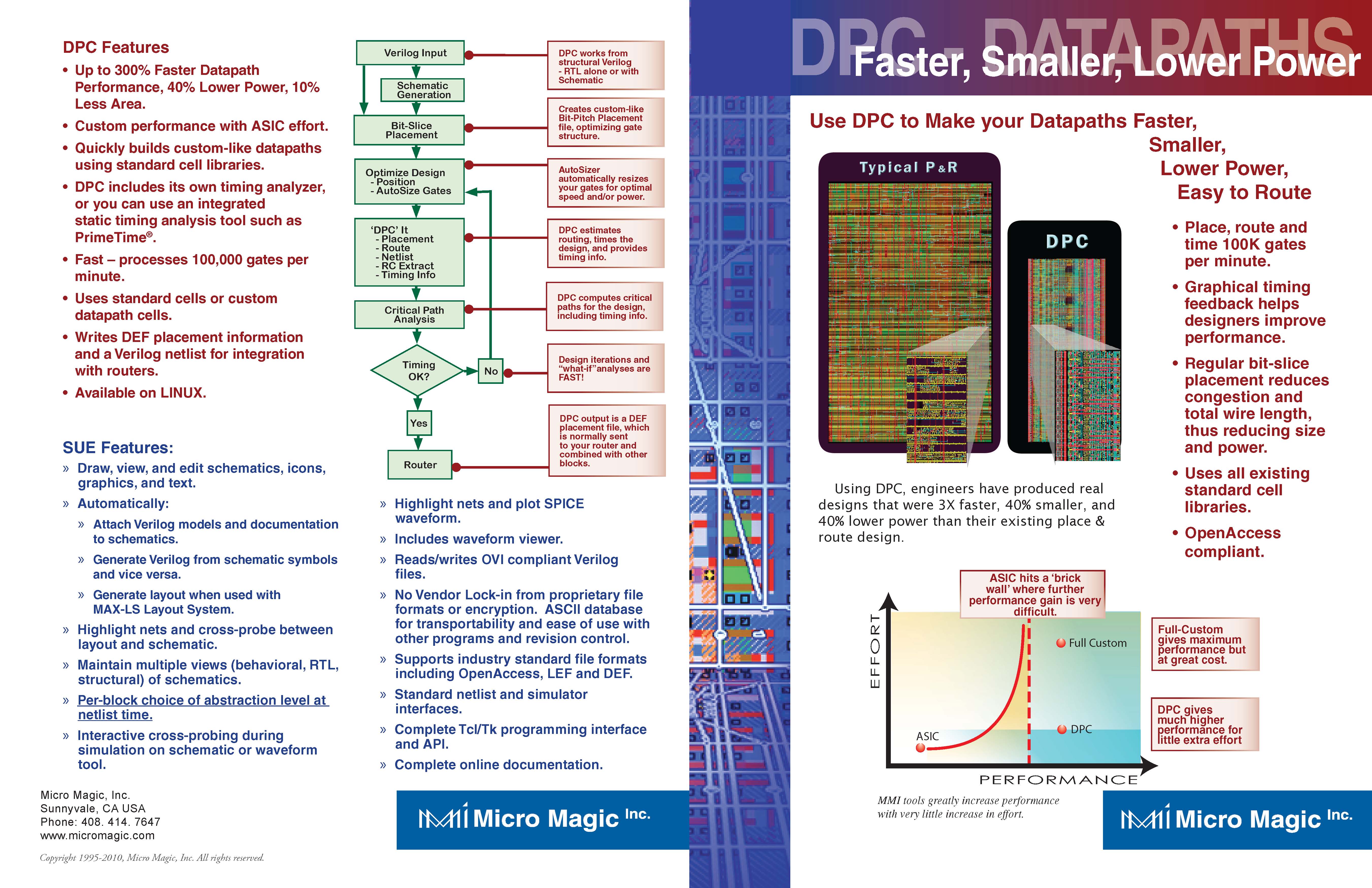

DPC for Datapaths Faster, Smaller, Lower Power, Easier routing

Micro Magic's DPC Datapath Compiler can place, route and time 100K gates/min. DPC will analyze congestion, and generates a custom-like bit-slice placement to improve timing and routing.More on DPC...

MAX-3D Path Finder Quickly and Automatically evaluate viability of 3D

Path Finder helps determine whether 3D TSV wafer stack is the best solution for your project. Use MAX-3D Path Finder to analyze partitioning, extract and simulate 3D nets, and generally explore the viability of an interposer or stacked-die implementation.More on Path Finder...

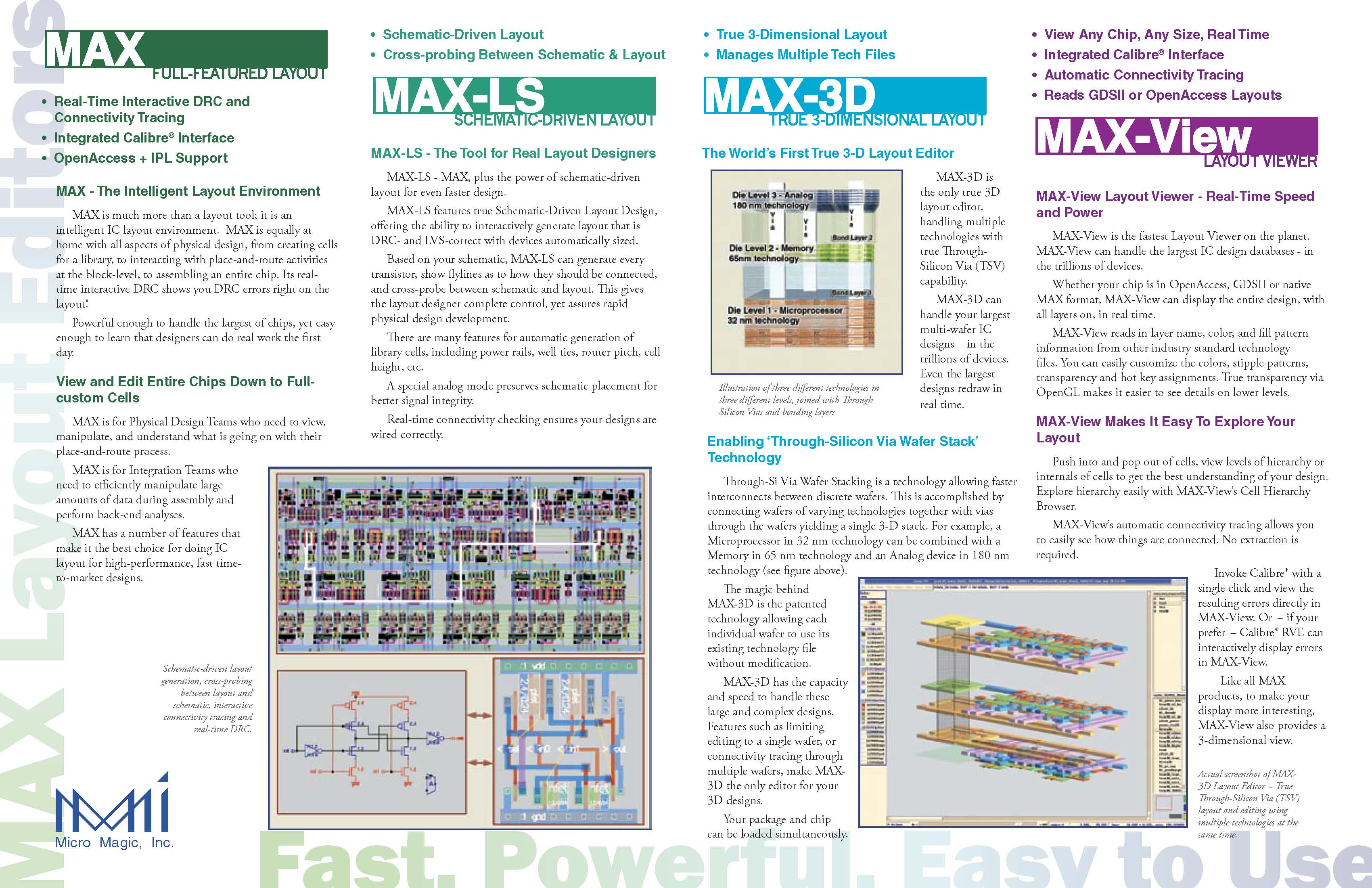

MAX-3D Layout The tool for true 3-Dimensional Layout

Load multilple chips/wafers and maintain distinct tech files for each layer. Full-featured editing for each tech file with real-time redisplay.More on MAX-3D ...

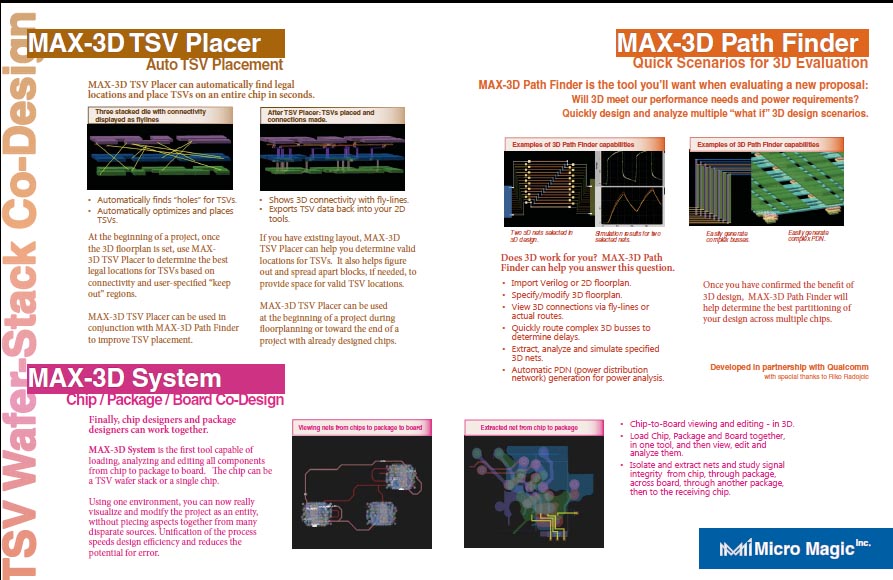

MAX-3D TSV Placer Automatic TSV Location, Optimization and Placement

MAX-3D TSV Placer scans your multi-level layout for optimal legal TSV placement. You can also adjust layout and insert blocking layers to modify placements if required. More on TSV Placer...

MAX-3D System The tool for chip/package/board co-design.

MAX-3D System enables you to view, edit and analyze multiple wafers/layers of one chip stack up thru the package and across the board to another chip stack. More on MAX-3D System...

to import designs from either 2D floorplanner or block-level verilog; specify chip level, block size, connectivity; and export floorplan to MAX-3D.

to explore viability of interposer or stacked-die implementations. Do multiple "what-if" studies on many different partitions.

for true 3-dimensional layout, supporting multiple distinct technooogy files for Through-Si Via 3D wafer-stack and interposer designs.

for automaticfally locating, optimizing and placing TSVs.

for the first time - your chips, package and PC board all together, in one tool. View, analyse & edit all of them in one environment. Isolate and extract nets; study signal integrity across all components.

“Tezzaron has taped out over 100 3D chips using MMI’s MAX-3D tool suite. There’s nothing to compare, and the new TSV placer & MAX-3D Path Finder are incredible.”

Robert Patti, VP/CTO, Tezzaron Semiconductor

“This is one of the few tools that can deal with multiple levels of hierarchy and multiple tech files all at the same time, and it is awesome for visualization of complex things like, say, PDN mesh across multiple die and interposers. Fantastic! I like it!”

Riko Radojcic, Director of Design for Silicon Initiatives, Qualcomm